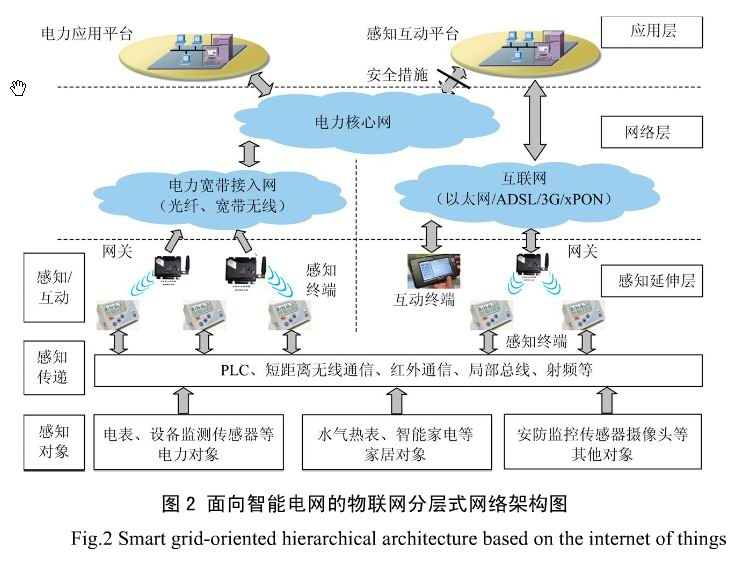

ARM体系结构

ARM是“先进的RISC机器(advancedRISCmachine)”的简写。ARM7使用vonNeumann构架,ARM9使用耶鲁构架(Harvardarchitecture)。ARM构架的帧率低,容积小。ARM有8,16,32和64位系统。使用基于RISC的计算机设计方式,ARM处理器所需的晶体管数目远远多于传统台式计算机或服务器中常见的×86CISC处理器的。这些技巧的用处是成本更低,热量更少,帧率更低,这种特点适用于轻便,便携,电瓶供电的设备,如智能手机和平板笔记本等中的应用。

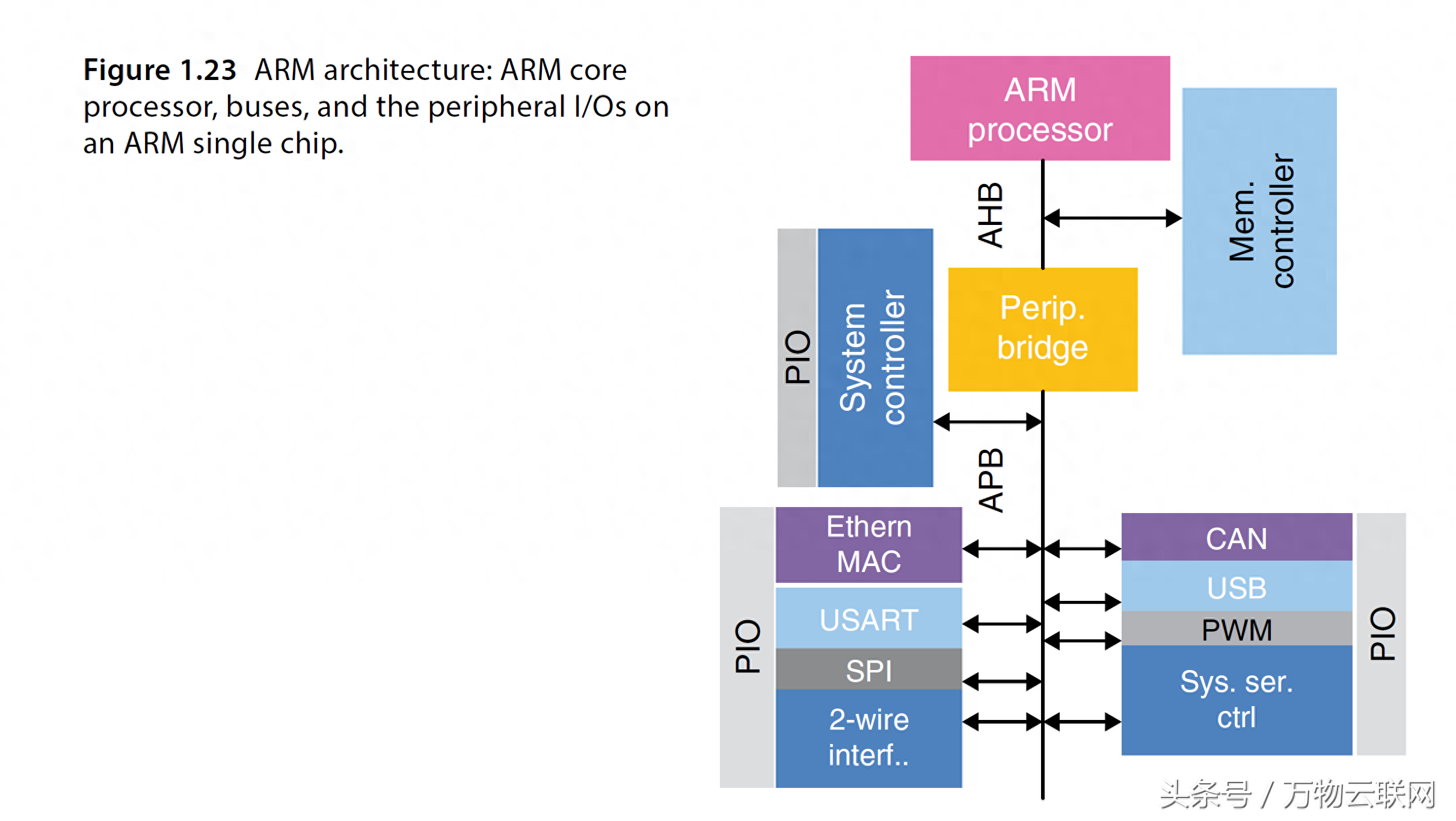

基于ARM的处理器包括Qualcomm(联发科)的Snapdragon(高通)处理器,Samasung的Exynos,nVidia的Tegra,Intel/Marvell的Xscale,TexasInstruments的OMAP,以及ARM的Cortex系列以及Apple用于iPhone和iPad产品中的Apple的A系列(比如,A7,A8)处理器。近来,英特尔通过降低AtomTM业务加入到了联通处理器芯片市场的竞争中。基于ARM的处理器一般在单个芯片上制造,其外围I/O称为片上系统或SoC。ARM处理器的体系结构如图1.23所示。

图1-23

图1.23ARM构架:ARM单核芯片上的ARM核处理器,总线和外设I/O.

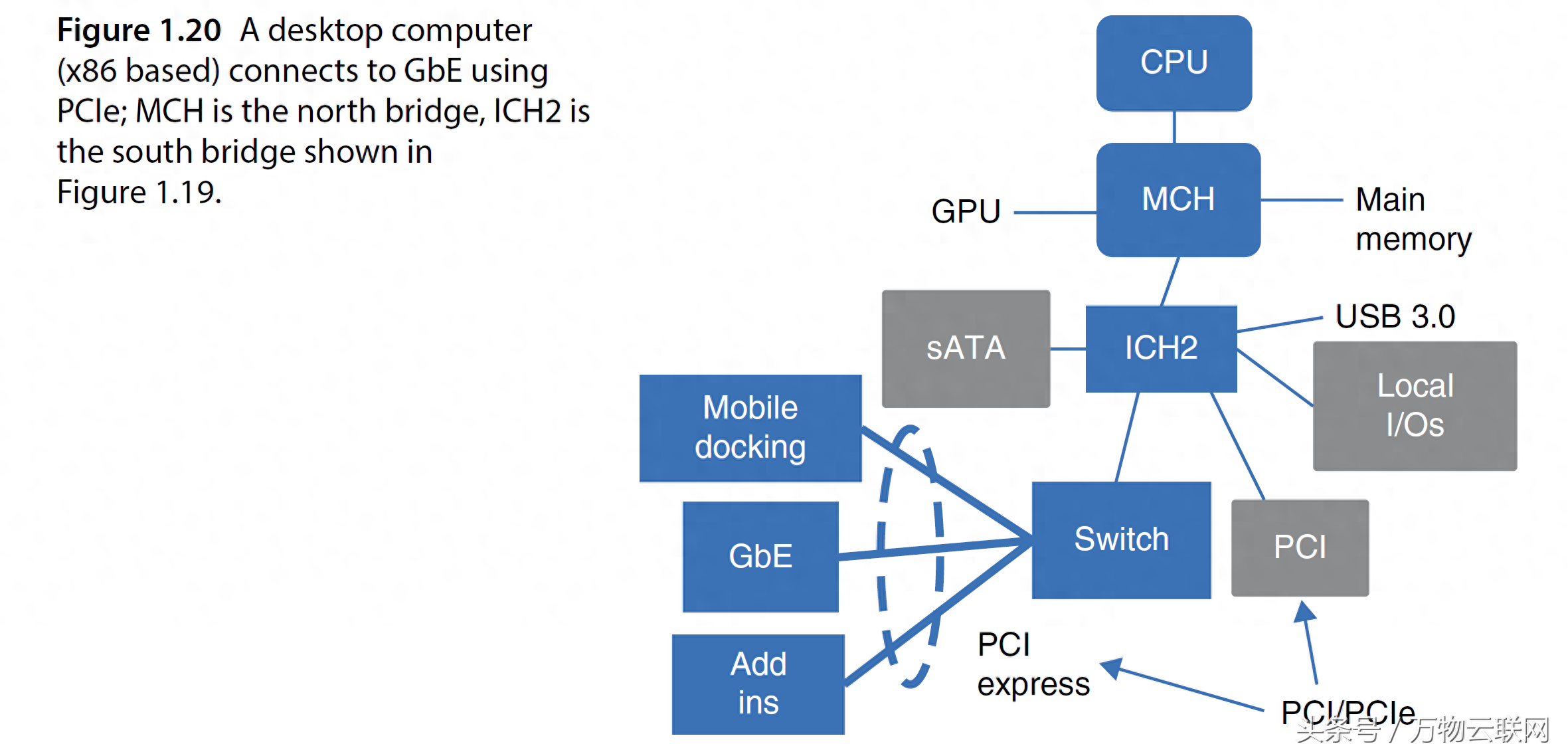

ARM中使用的AMBA(先进的微控制器总线构架,advancedmicrocontrollerbusarchitecture)是一种开放式标准总线。它有两种总线构架:AMBA高性能总线(AHB,AMBAhigh‐performancebus)和AMBA外设总线(APB,AMBAperipheralsbus)。AHB通过显存控制器与显存进行通讯;APB联接到外设桥以后的“简单”外设I/O(图1.23中的PIO)。图1.23所示的总线结构比图1.19和1.20所示的南桥和北桥简单得多。请注意ARM单芯片的构架功能块上的诸多外设I/O.在TIOMAP4530上,也是基于ARM的单芯片,有许多外围I/O:USARTlinux系统介绍,GPIP,I2C/SPI。这种I/O用于联接许多外围设备,比如收发器IC红旗linux下载,基带IC,wifi/蓝牙联接RF模块,陀螺仪和加速度计,触摸屏和控制器。

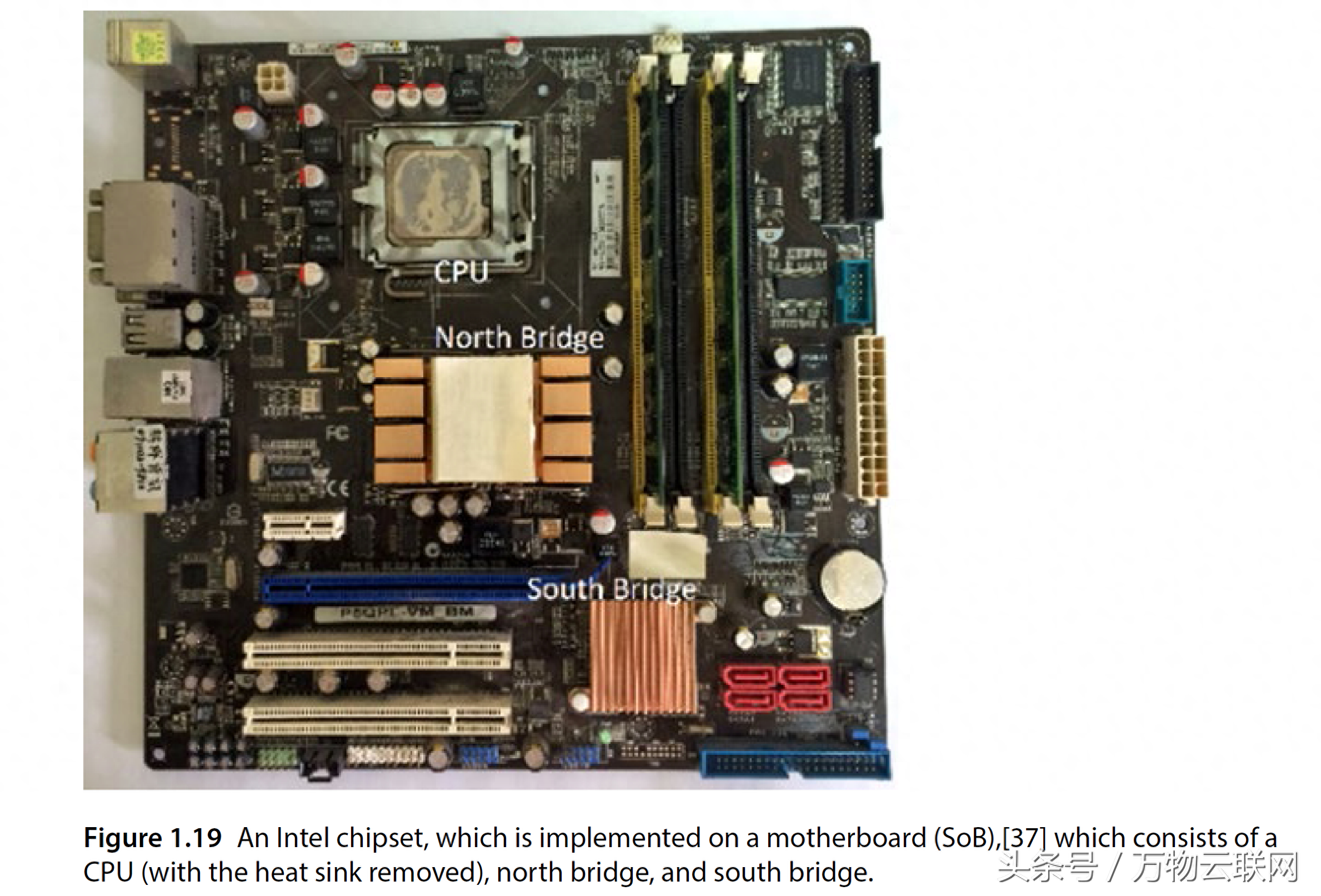

图1-19

图1.19英特尔芯片组,在显卡(SoB)上实现,由CPU(移除散热器),南桥和北桥组成。

图1-20

图1.20台式计算机(基于x86)使用PCIe联接到GbE;MCH是南桥,ICH2是北桥,如图1.19所示。

与图86中的×86完全不同的另一个特点是ARM构架中的GPU坐落处理器内部。也就是说,它是一种集成图形解决方案的方式。

其他重要的共同特点是基于ARM的单芯片主要面向联通用户,由于它们的帧率较低,无论是标准的还是订制的。基于ARM的单芯片的帧率一般高于1W。并且,在智能手机(iPhone或Android手机)中,帧率最大的设备可能不是基于ARM的应用处理器;相反,它可能是4GRF收发器(如Qualcomm的RTR8600)中的PA模块或显示处理器。每位平均可能超过2瓦(33dBm)。

无线广域网

如今让我们将注意力转向实现个人联通性的主要设备:联通设备或联通电话。在下边的部份中,我们将介绍蜂窝电话的体系结构,它将主要功能分解为几个块。而且linux 9x25 spi驱动移植,我们将讨论每位块中使用的组件。

近来,4GLTE在新加坡上市。LTE是用于联通电话和数据终端的高速数据的无线通讯的标准。它基于GSM/EDGE和UMTS/HSPA网路技术。它采用不同的无线电插口以及核心网路改进,以提升容量和速率。LTE是具有GSM/UMTS网路和CDMA的营运商的自然升级路径。理想情况下,4G网路可以实现下行链路100Mbits/s(Mbps),上行链路50Mbps。

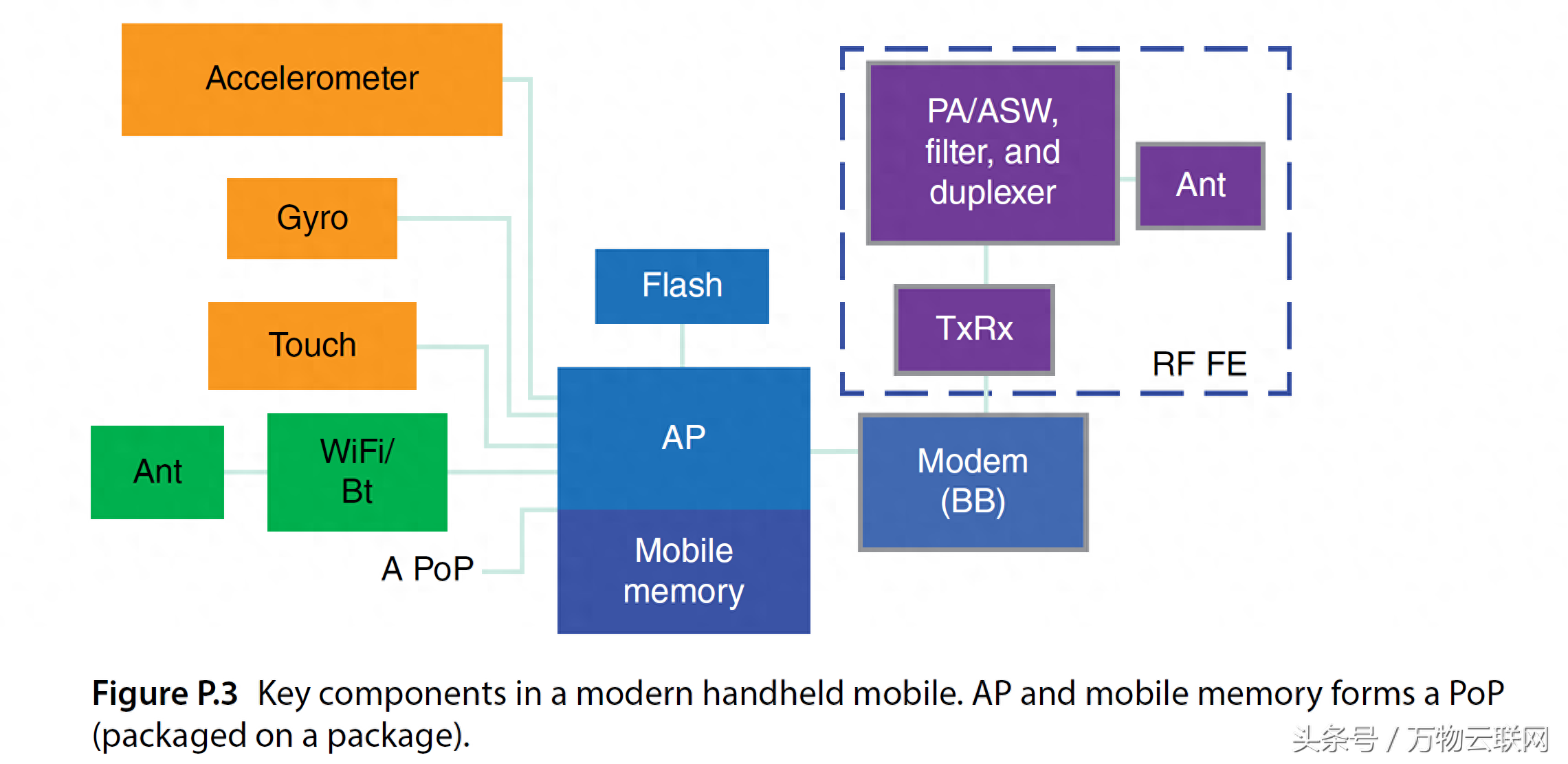

图P.3

图P.3现代手持联通设备中的关键组件。AP和联通储存器产生PoP(封装在封装上,packagedonapackage)。

按照拆解数据,用于作为4G联通设备的iPhone5的构架功能块可以在下边的图P.3中说明。最新的iPhone的拆解相片可以在网上找到。主要模块有:主处理器及其储存器,用于蜂窝通讯的RF(射频)后端,短距联接(wifi/蓝牙/无线电广播)的射频(RF)模块以及用户界面集成电路。没有显示单个最大的组件,电瓶。电瓶的重要性可能与其大小成反比,由于它为漫游提供动力,其容量与通话时间直接相关。

应用处理器(AP)及其主联通储存器

Apple(苹果公司)的A系列AP

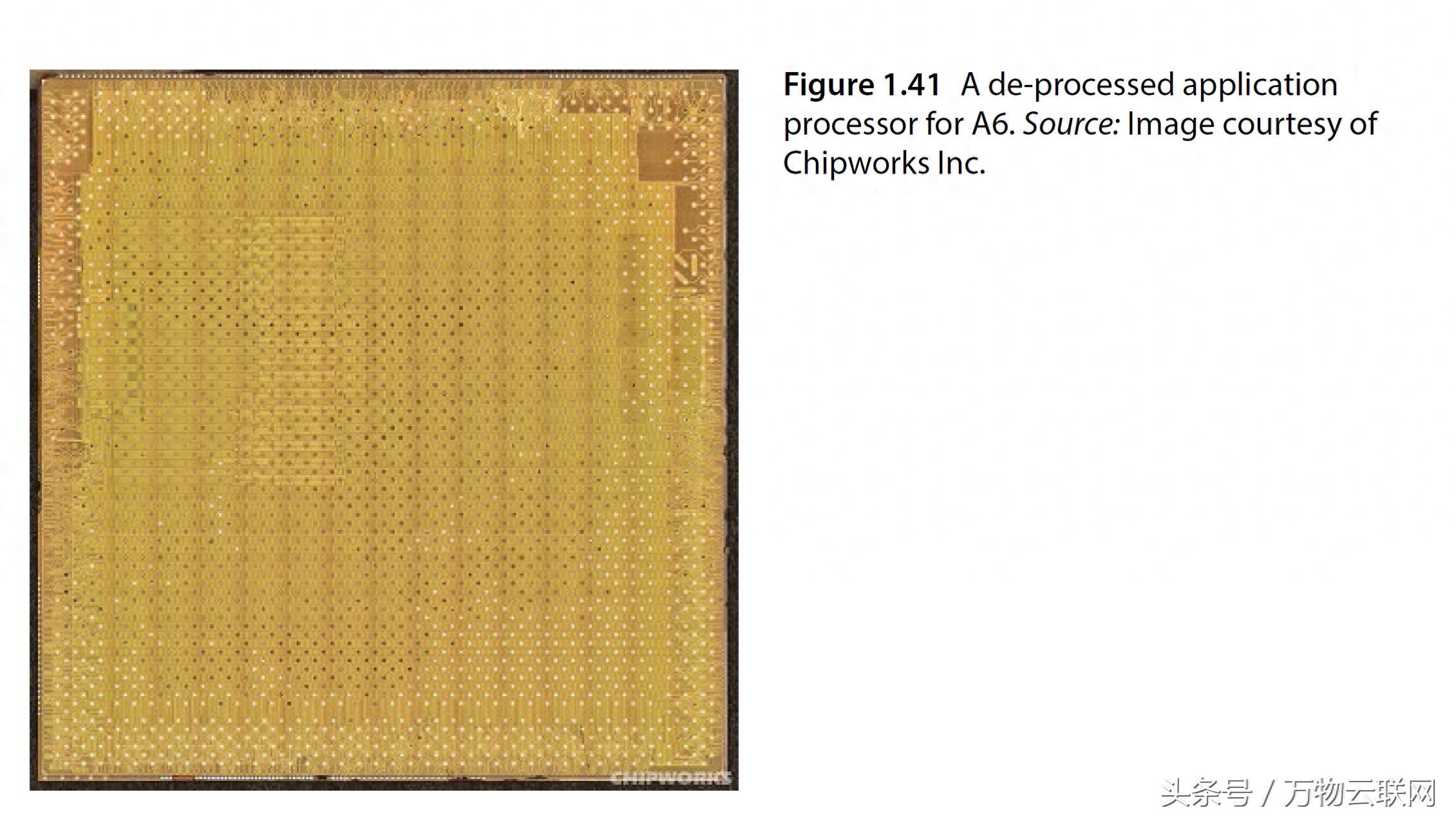

以Apple的iPhone5为例,该应用处理器是A6(如图1.41所示),它采用双ARM核和三核GPU制造,采用SoC实现。支持这种处理器的储存层包括高速缓存,寻址储器和外部NAND闪存。高速缓存储存器L1和L2在片上,寻址储器(1GBLPDDR)与A6应用处理器集成在一起,使用堆叠式封装或PoP技术。在iPhone5的主逻辑板上,提供了16GB或32GBNAND闪存的选择,并集成在电路板的另左侧。

图1-41

图1.41A6应用程序处理器。资料来源:图片提供ChipworksInc.

值得注意的是,在×86CPU中,图形处理器最初与CPU集成在一起,而且,当GPU成为主导时(因为联通设备上的图形演示需求),它在外部提供给×86CPU通过单独的GPU可插入板。GPU由×86板上的MCH管理。

联通显存LPDDR

JEDEC定义了LPDDR和宽I/O的标准,如LPDDR2(JESD209-2),LPDDR3(JESD209-3C),LPDDR4(JESD209-4)和宽I/O(JESD229),以及宽I/O2(JESD229-2)显存。Cadence早已发布了LPDDR5的模型。

冯·诺依曼构架下与ARM处理器紧密配合的储存器是联通设备中的重要单元。因为在×86和ARMSoC处理器中使用不同的电源,因而储存器的设计也必须不同。也就是说linux 9x25 spi驱动移植,例如LPDDR(低功率DDR,即联通DDR)的低功率系列用于联通设备。如上所述,应用处理器(比如,A7,A8)及其主联通储存器以PoP格式封装。一个GBLPDDR3已用于iPhone5S(A7)和iPhone6(A8)。三星制造的两台GBLPDDR4用于iPhone6S(四核,A9)和iPhoneSE。

JEDEC定义了LPDDR和宽I/O联通储存器的标准。有关联通储存器的更多讨论,敬请关注。

(完)